Flip-flop je termín, ktorý patrí pod digitálnu elektroniku a je to elektronická súčiastka, ktorá sa používa na uloženie jedného bitu informácií.

Diagramové znázornenie Flip Flopu

- Pretože Flip Flop je sekvenčný obvod, jeho vstup je založený na dvoch parametroch, jeden je aktuálny vstup a druhý je výstup z predchádzajúceho stavu.

- Má dva výstupy, oba sa navzájom dopĺňajú.

- Môže byť v jednom z dvoch stabilných stavov, buď 0 alebo 1.

Základná schéma Flip Flop

Čo je T Flip Flop?

- T flip flop alebo presnejšie je známy ako Toggle Flip Flop, pretože dokáže prepínať svoj výstup v závislosti od vstupu.

- T tu znamená Prepnúť .

- Prepínač v podstate znamená, že bit bude prevrátený, t. j. buď z 1 na 0, alebo z 0 na 1.

- Tu je na ovládanie tohto flopu dodávaný hodinový impulz, teda ide o taktovaný klopný obvod.

Konštrukcia T Flip Flop

T flip môžeme skonštruovať tromi spôsobmi, a to:

- Pomocou SR Flip Flops.

- Pomocou D Flip Flops.

- Pomocou JK Flip Flops

Spôsoby konštrukcie T Flip Flop

Pozrime sa na konštrukciu T Flip Flop pomocou SR Flip Flops, ktoré vyžadujú 2 AND brány a 2 NOR brány, ako je uvedené nižšie:

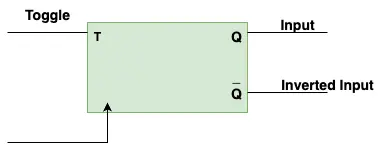

Základná bloková schéma T Flip Flop

Bloková schéma tu obsahuje prepínacie a hodinové vstupy, Q a Q' sú doplnené vstupy.

Fungovanie T Flip Flop

Prípad 1 : Povedzme, T = 0 a hodinový impulz je vysoká tj 1, potom bude výstup oboch hradla AND 1 a hradla AND 2 0 , brána 3 výstup bude Q a podobne brána 4 výstup bude Q' takže obidve hodnoty Q a Q' sú rovnaké ako ich predchádzajúca hodnota, čo znamená Držte stav .

Prípad 2 : Povedzme, T = 1 , potom bude výstup oboch hradel AND 1 (T * hodiny * Q) , a keďže T aj hodiny sú 1, potom výstup AND hradla 1 bude Q , a podobne bude výstup AND hradla 2 (T * hodiny * Q') t.j. Q' . Teraz bude výstup brány 3 (Q'+Q)' a povedzme, že Q' je nula, potom bude výstup brány 3 (0+Q)“ čo znamená Q' a podobne bude výstup brány 4 (Q+Q’)“ a keďže Q' je nula, výstup brány 4 bude Q', čo znamená 0 pretože Q' je nula. Preto v tomto prípade môžeme povedať, že výstup sa prepína, pretože T = 1 .

Tabuľka pravdy T Flip Flop

- Tu je T prepínací vstup, Q je vstup súčasného stavu, Qt+1 je výstup ďalšieho stavu.

- Odtiaľ môžeme vidieť, že kedykoľvek je Toggle (T) 0, výstup ďalšieho stavu (Qt+1) je rovnaký ako vstup aktuálneho stavu (Q).

- Vždy, keď je prepínač (T) 1, výstup nasledujúceho stavu (Qt+1) bude doplnkom vstupu aktuálneho stavu (Q), čo znamená, že sa prepne.

Charakteristická rovnica

- Charakteristická rovnica nám hovorí o tom, aký bude ďalší stav klopného obvodu z hľadiska súčasného stavu.

- Na získanie charakteristickej rovnice sa vytvorí mapa K, ktorá bude znázornená nižšie:

- Ak vyriešime vyššie uvedenú K-mapu, potom bude charakteristická rovnica Q(n+1) = TQn’ + T’Qn = T XOR Qn

Tabuľka budenia

Tabuľka budenia v podstate hovorí o budení, ktoré vyžaduje klopný obvod na prechod z aktuálneho stavu do nasledujúceho stavu.

- Vždy, keď je T 0, Qt+1 je rovnaké ako vstup Q.

- A kedykoľvek je T 1, Qt+1 je kompliment vstupu Q.

Aplikácie T Flip Flop

V digitálnom systéme existuje množstvo aplikácií T Flip Flop, ktoré sú uvedené nižšie:

- Počítadlá : T Flip Flops používané v pultoch. Počítadlá počítajú počet udalostí, ktoré sa vyskytnú v digitálnom systéme.

- Úložisko dát : T Flip Flops používané na vytvorenie pamäte, ktorá sa používa na ukladanie dát, keď je napájanie vypnuté.

- Synchrónne logické obvody : T klopné obvody možno použiť na implementáciu synchrónnych logických obvodov, čo sú obvody, ktoré vykonávajú operácie s binárnymi údajmi na základe hodinového signálu. Synchronizáciou operácií logického obvodu s hodinovým signálom pomocou T klopných obvodov môže byť správanie obvodu predvídateľné a spoľahlivé.

- Frekvenčné delenie : Používa sa na delenie frekvencie hodinového signálu 2. Flip-flop prepne svoj výstup zakaždým, keď hodinový signál prejde z vysokej na nízku alebo z nízkej na vysokú, čím sa hodinová frekvencia vydelí 2.

- Posunové registre : T klopné obvody možno použiť v posuvných registroch, ktoré sa používajú na posun binárnych údajov jedným smerom.

Záver

V tomto článku začíname od základov žabiek, čo sú vlastne žabky, a potom sme diskutovali o žabkách T, troch dvoch spôsoboch, ktorými môžeme skonštruovať žabky T, je to základný blokový diagram, fungovanie T žabiek , je to tabuľka pravdy, charakteristická rovnica ako aj tabuľka excitácie a na záver sme diskutovali o aplikáciách T Flip Flops.